VLSI-课程部分知识点

Lecture1 Introduction

介绍下常见的几个指令集

- MIPS, Microprocessor without Interlocked Pipeline Stages, 一种精简指令集计算 (RISC) 架构, 广泛用于嵌入式系统和网络设备

- x86, 复杂指令集计算 (CISC) 架构, 主要用于个人电脑和服务器, 支持丰富的指令集和高兼容性

- Alpha, 由数字设备公司 (DEC) 开发的RISC架构, 以其高性能和64位支持著称, 但已不再更新

- PIC, Peripheral Interface Controller, 一种微控制器架构, 主要用于嵌入式应用, 具有低功耗和高效率的特点

- ARM, Advanced RISC Machine, 一种流行的RISC架构, 以其高能效和小尺寸而闻名, 广泛用于移动设备和嵌入式系统

Pipline

在现代处理器中,指令通常被拆解为多个步骤 (如取指, 译码, 执行, 写回), 这些步骤被视为流水线中的不同阶段, 多个指令在不同阶段同时执行, 以提高处理效率. 这类似于工厂的生产线, 每个阶段并行工作, 提高指令吞吐量.

举个例子, 假设对一个指令的处理分 5 个阶段:

- IF (Instruction Fetch): 取指令

- ID (Instruction Decode): 译码并读取寄存器

- EX (Execute): 执行运算或内存地址计算

- MEM (Memory Access): 访问数据存储器(如加载或存储数据)

- WB (Write Back): 将结果写回寄存器

一段指令如下:

1 | |

如果没有流水线, 则是串行执行, 一个指令处理完之后, 再处理下一个指令, 那么这几条指令的耗时为:

1 | |

而如果是流水线执行, 在 ADD 指令从 IF 到 ID 之后, SUB 指令就会开始 IF 阶段的处理, 总的可以描述为:

| 周期 | ADD | SUB | LOAD | STORE |

|---|---|---|---|---|

| 1 | IF(ADD) | |||

| 2 | ID(ADD) | IF(SUB) | ||

| 3 | EX(ADD) | ID(SUB) | IF(LOAD) | |

| 4 | MEM(ADD) | EX(SUB) | ID(LOAD) | IF(STORE) |

| 5 | WB(ADD) | MEM(SUB) | EX(LOAD) | ID(STORE) |

| 6 | WB(SUB) | MEM(LOAD) | EX(STORE) | |

| 7 | WB(LOAD) | MEM(STORE) | ||

| 8 | WB(STORE) |

此时总耗时为 8 个周期, 效率高很多.

流水线数据依赖和互锁

流水线中的一条指令的执行结果被后续指令需要, 因此, 后续指令需要等待前面指令执行结束之后才能进行后续操作.

举个例子:

1 | |

在这个例子中, 第二条指令依赖于第一条指令的结果 (R1), 因此第二条指令不能在第一条指令完成之前执行.

互锁流水线阶段, interlocked pipeline stages, 指处理器会自动暂停后续指令, 直到依赖的数据准备好. 这种互锁机制通过硬件实现, 可以避免手动插入等待的指令, 从而简化编程.

而无互锁的流水线, 虽然减少了硬件复杂度, 但是会增加程序员和编译器的负担.

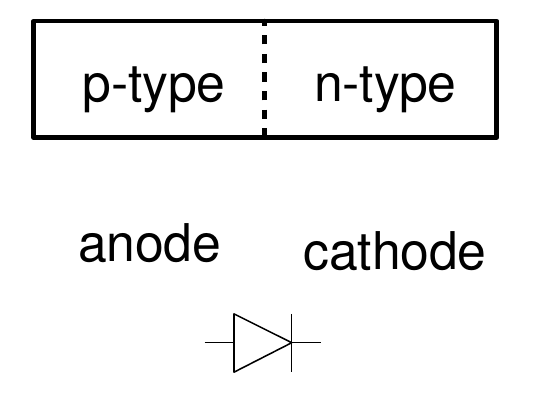

掺杂的目的

形成 PN Junction, 让电流单向流动:

NMOS 和 PMOS 的真值表

| Input | NMOS | PMOS |

|---|---|---|

| 0 | OFF | ON |

| 1 | ON | OFF |

此时已经可以把两者当作 switch 了.

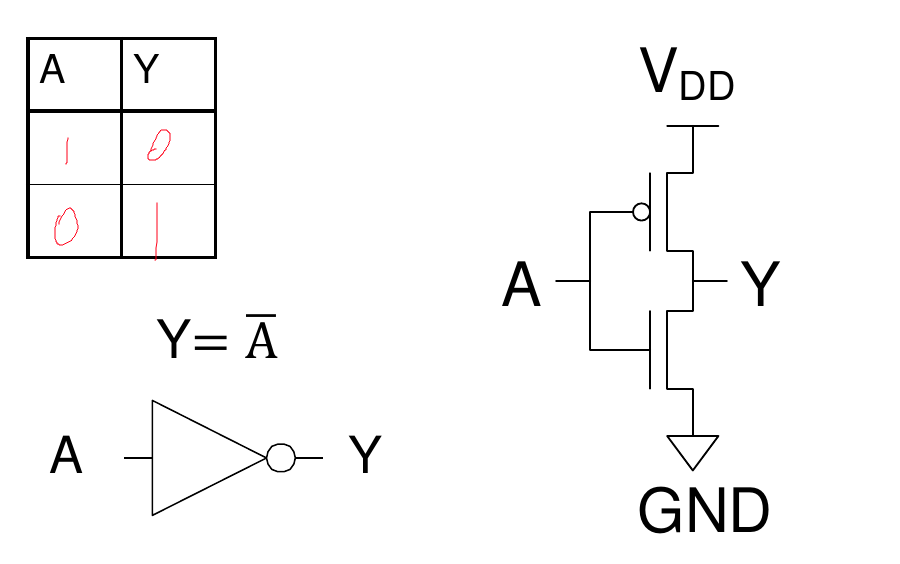

CMOS Inverter

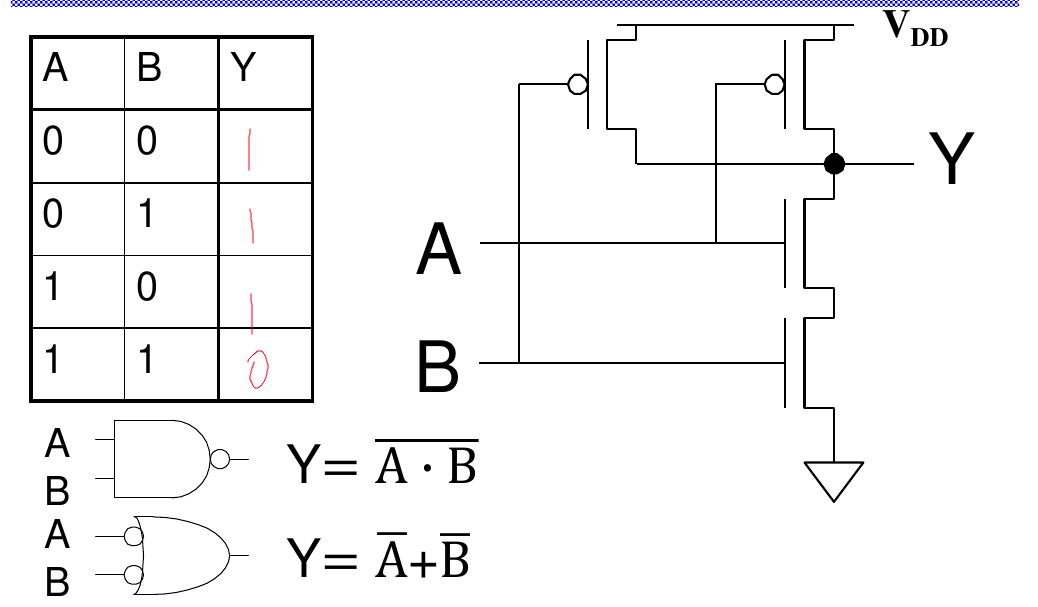

CMOS NAND

有 0 就有 1:

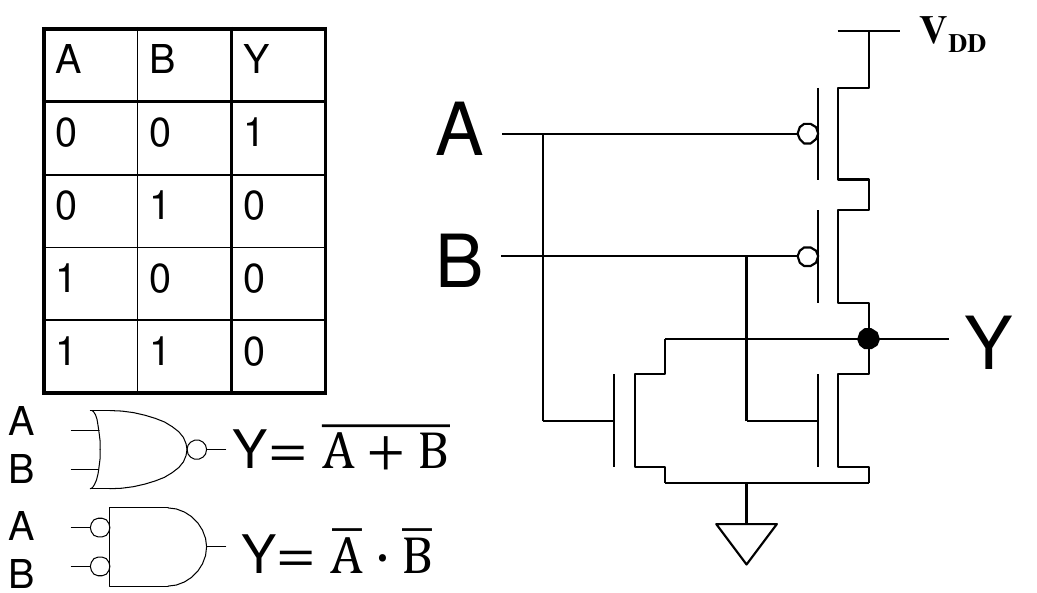

CMOS NOR

有 1 就有 0:

UV light 和 EUV

UV 指 Ultraviolet light, 即紫外线, 波长比可见光中的紫光短.

EUV 指 Extreme Ultraviolet light, 波长极短的紫外光, 能量更高. 能够实现更高的分辨率和更精细的加工.

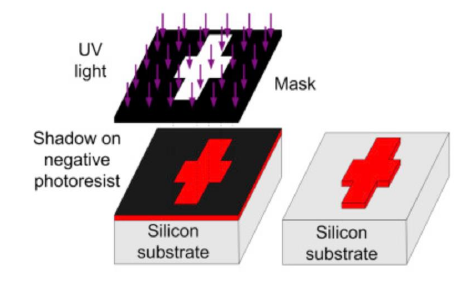

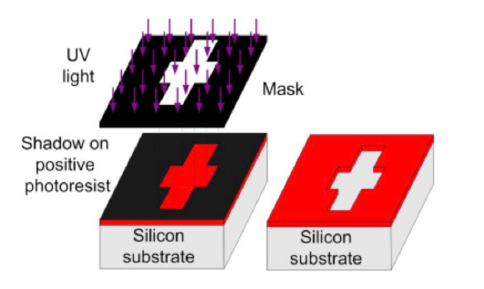

Photoresit

分两种:

negative, 光照的部分 harden

positive, 没被光照的部分 harden

well 和 tap

well 指掺杂的区域, tap 指接地点.

well-tap 指连接到 n-well 或 p-well 的接地点.

substrate tap 指基底的接地点.

Lecture2 Circuits & Layout

NRE costs 和 Recurrent costs

NRE costs 指是在产品开发阶段产生的一次性工程费用. 这些费用在产品的整个生命周期内只发生一次, 主要包括设计, 研发, 原型制作, 测试和验证等活动的成本. 这些成本不会随着每个产品的生产重复发生, 因此称为 “非重复性工程成本”.

Recurrent costs 指在产品生命周期内会定期或持续发生的费用. 这些成本通常与产品的生产, 运营, 维护和支持相关, 且会随着生产数量或时间周期的增加而增加.

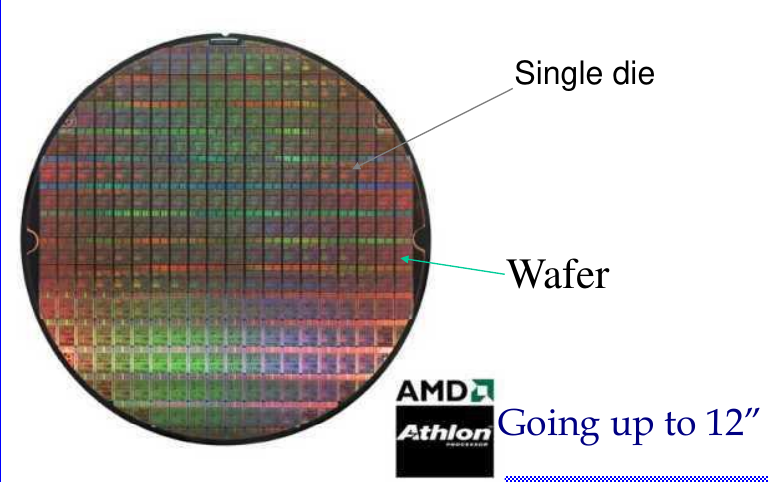

Die cost

Die Cost (芯片单元成本) 是指从一片**硅晶圆 (wafer) 中制造出的单个裸片 (die)**的平均成本. 这是芯片制造中的一个关键指标, 直接影响半导体产品的最终价格.

Yield

Yield, 指良率, 表示在整个制造过程中生产出合格产品的比例. 计算为:

$$

\displaylines

{

\begin{aligned}

Y = \frac{No.\ of\ good\ chips\ per\ wafer}{Total\ number\ of\ chips\ per\ wafer} \times 100%

\end{aligned}

}

$$

Die cost 可以计算为:

$$

\displaylines

{

\begin{aligned}

Die\ cost = \frac{Wafer\ cost}{Dies\ per\ wafer \times Die\ yield}

\end{aligned}

}

$$